Intel 8085

| 此條目可參照英語維基百科相應條目來擴充。 (2020年8月5日) |

一種帶有黑色塑料和銀色引腳的Intel P8085AH-2處理器變體。 | |

| 產品化 | 1976年3月至2000[1] |

|---|---|

| 生產商 | |

| 指令集架構 | 8085 |

| 製作工藝/製程 | 3 µm |

| CPU主頻範圍 | 3, 5, 6 MHz |

| CPU插座 | |

| 封裝 |

|

| 上代產品 | Intel 8080 |

| 繼任產品 | Intel 8086 |

Intel 8085(「八-零-八-五」)是由Intel生產並於1976年3月[2]推出的8位微處理器。它是Intel開發的最後一個8位微處理器。

它與更著名的Intel 8080在軟體二進位兼容性上相同,只增加了兩個小指令以支持其新增的中斷和串行輸入/輸出功能。然而,它需要的支持電路較少,使得可以構建更簡單、成本更低的微型計算機系統。

部件編號中的「5」突出顯示了8085使用單一+5伏(V)電源供電的事實,它使用耗盡模式電晶體,而不需要8080所需的+5 V、-5 V和+12 V電源。這種能力與競爭對手Z80匹配,Z80是一款流行的8080衍生CPU,於前一年推出。這些處理器可用於運行CP/M作業系統的計算機。

8085採用40針DIP封裝供應。為了在可用引腳上最大化功能,8085使用多路復用(AD0-AD7)匯流排。然而,一個8085電路需要一個8位地址鎖存器,因此Intel製造了幾種帶有內置地址鎖存器的支持晶片。這些包括帶有地址鎖存器、2 KB EPROM和16個I/O引腳的8755,以及帶有256位元組RAM、22個I/O引腳和一個14位可程式定時器/計數器的8155。復用地址/數據匯流排減少了在8085與這些內存和I/O晶片之間PCB走線數量。

8080和8085都被Zilog Z80超越,在桌面計算機領域使用Z80取得了大部分CP/M計算機市場,並且在1980年代初到中期迅速發展的家用計算機市場也占有一席之地。

由於其內置串行I/O和五個優先級中斷——可以說是類似微控制器的特性(這些是Z80 CPU所沒有的),8085作為控制器具有很長壽命。自從20世紀70年代末設計用於DECtape II控制器和VT102視頻終端等產品之後,在這些產品生命周期內一直進行新生產。通常來說,這比桌面計算機產品壽命要長得多。

描述[編輯]

8085 是基於 Intel 8080 的傳統馮·諾依曼設計。與 8080 不同的是,它沒有將狀態信號復用到數據匯流排上,而是將 8 位數據匯流排與 16 位地址匯流排的低八位復用,以將引腳數量限制在 40 個。狀態信號由專用的匯流排控制信號引腳和兩個專用的匯流排狀態 ID 引腳 S0 和 S1 提供。第 40 腳用於電源供應(+5 V),第 20 腳用於接地。第 39 腳被用作保持引腳。

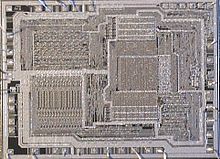

該處理器採用 nMOS 電路設計,後來的「H」版本採用了 Intel 稱為 HMOS II(「高性能 MOS」)的增強型 nMOS 工藝實現,最初是為快速靜態 RAM 產品開發的。[3]只需要單一的 5V 電源供電,與競爭處理器一樣,不同於8080。8085 使用大約6500個電晶體。[4]

8085 集成了8224(時鐘生成器)和8228(系統控制器)的功能,提高了集成度。與同時期類似設計(如 Z80)相比的一個缺點是匯流排需要解復用;然而,在Intel 的8155、8355 和8755 存儲晶片中的地址鎖存器允許直接接口,因此一個8085連同這些晶片幾乎可以組成一個完整系統。

8085 擴展了對新中斷的支持,有三個可屏蔽向量中斷(RST7.5、RST6.5 和 RST5.5),一個不可屏蔽中斷(TRAP),以及一個外部服務中斷(INTR)。這五種中斷每種都有處理器上的單獨引腳,這一特性使得簡單系統可以避免額外購買獨立中斷控制器的成本。RST7.5 中斷是邊緣觸發(鎖存)的,而 RST5.5 和 RST6.5 是電平敏感型。除 TRAP 外所有中斷都可通過 EI 指令啟動並通過 DI 指令禁止。此外,SIM (設置中斷掩碼) 和 RIM (讀取中斷掩碼) 指令——這兩條指令是8080 設計之外唯二新增加到8085 的指令——允許分別屏蔽三個可屏蔽 RST 中斷。正常 CPU 復位後所有三個都會被屏蔽。SIM 和 RIM 還可以讀取全局中斷掩碼狀態和三個獨立 RST 中斷掩碼狀態、讀取這三個相同中斷待處理狀態、重置 RST7.5 觸發鎖存觸發器(取消待處理中斷而無需處理它),並且還可以通過 SOD 和 SID 引腳分別發送和接收串行數據,並且所有操作都能在程序控制下獨立進行。

SIM 和 RIM 每條執行四個時鐘周期(T 狀態),使得可能比通過任何 I/O 或內存映射埠切換或採樣信號更快地採樣 SID 或/及切換 SOD。(因此 SID 可以與6502 CPU 當時代表性產品 SO ["Set Overflow"] 引腳進行比較)

像8080一樣,8085可以通過外部生成的等待狀態(第35腳,READY)來適應慢速內存,並具備使用HOLD和HLDA信號(第39和38腳)進行直接內存訪問(DMA)的功能。與8080相比的一個改進是,8085可以直接驅動與其直接連接的壓電晶體,並且內置時鐘發生器在晶體頻率的一半產生高幅度的雙相時鐘信號(例如,6.14 MHz的晶體將產生3.07 MHz的時鐘)。內部時鐘可在一個輸出引腳上獲取,用於驅動外圍設備或其他CPU,使其與輸出該信號的CPU保持步調一致。8085也可以由外部振盪器提供時鐘(這使得使用系統範圍內共用時鐘的同步多處理器系統中使用8085成為可能,或者將CPU同步到外部時間參考,如視頻源或高精度時間參考)。

8085是與8080二進位兼容的後續產品。它支持8080的完整指令集,並且指令行為完全相同,包括對CPU標誌位的所有影響(AND/ANI操作除外,該操作設置AC標誌位不同)。這意味著絕大多數在8080上成功運行的目標代碼(ROM或RAM中任何程序鏡像)都可以直接在8085上運行,無需翻譯或修改。(例外包括對時間敏感的代碼以及對前述AC標誌位設置差異或未記錄CPU行為差異敏感的代碼。)[5]8085指令時序略有不同於8080——一些8位操作,包括INR、DCR和廣泛使用的MOV r,r' 指令比原來快一個時鐘周期,但涉及16位操作的指令包括堆疊操作(增減16位SP暫存器),通常慢一個周期。當然,在實際情況下 8080 和/或 8085 可能與發布規格尤其是微小細節有所不同。(Z80則不然)。如前所述,只有SIM和RIM指令是8085新增加的。

| 這是一篇與微電腦或微處理器相關小作品。你可以透過編輯或修訂擴充其內容。 |

| |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

- ^ The Life Cycle of a CPU. www.cpushack.com.

- ^ Intel® Microprocessor Quick Reference Guide - Year. www.intel.com.

- ^ Intel Corporation, "New Products: HMOS MCS-85 Chips Uses 20 to 30 Percent Less Power", Solutions, July/August 1981, Page 22

- ^ The history of the microcomputer-invention and evolution, S Mazor - Proceedings of the IEEE, 1995

- ^ The MCS-80/85 Family User's Manual (PDF). Intel. January 1983. pp. 1–8. (原始內容存檔 (PDF)於2017-08-29).

The 8085A CPU is 100% software compatible with the Intel 8080A CPU.