反或閘

| 基本邏輯閘 | |

| 緩衝 | 非 |

| 及 | 反及 |

| 或 | 或非 |

| 互斥或 | 同或 |

| 蘊含 | 蘊含非 |

| 輸入 A B |

輸出 A NOR B | |

| 0 | 0 | 1 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 0 |

反或閘(英語:NOR gate)是數位邏輯中實現邏輯或非的邏輯閘,功能見右側真值表。若輸入均為低電平(0),則輸出為高電平(1);若輸入中至少有一個為高電平(1),則輸出為低電平(0)。或非是邏輯或加邏輯非得到的結果。或非是一種具有函數完備性的運算,因此其他任何邏輯函數都能用反或閘實現。相比之下,邏輯或運算器是一種單調的運算器,其只能將低電平變為高電平,但不能將高電平變為低電平。

在絕大多數但不是所有的電路設計中,邏輯非的功能本身就包含在結構中,如CMOS和TTL等。在這樣的邏輯系列中,要實現或閘,唯一的方法是用2個或更多的邏輯閘來實現,如一個反或閘加一個反相器,但一個重要的例外是多米諾邏輯,因為其結構中本身就沒有反相邏輯。

概述[編輯]

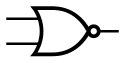

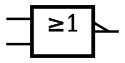

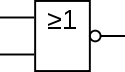

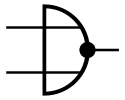

下列包括邏輯閘的3種符號:形狀特徵型符號(ANSI/IEEE Std 91-1984)、IEC矩形國標符號(IEC 60617-12)和不再使用的DIN符號(DIN 40700)。其他的邏輯閘符號見邏輯閘符號表。

| 表達式 | 符號 | 功能表 | 繼電器邏輯 | ||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ANSI/IEEE Std 91-1984 | IEC 60617-12 | DIN 40700 | |||||||||||||||||||||||

|

|

|

|

| |||||||||||||||||||||

硬體描述和引腳分配[編輯]

反或閘是基本的閘電路,因此常用於電晶體-電晶體邏輯(TTL)和CMOS積體電路。標準4000系列CMOS積體電路是4001,包含四個2輸入反或閘。引腳分配如下:

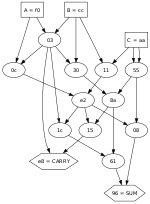

|

|

可用型號[編輯]

大多數半導體製造商都生產這種元件,如快捷半導體公司、飛利浦、德州儀器,封裝方式分為直插DIP封裝和SOIC封裝兩種。元件的數據表可在大多數元件資料庫查詢到。

常用的CMOS和TTL邏輯系列中,也有8輸入反或閘:

- CMOS

- 4001:四2輸入反或閘

- 4025:三3輸入反或閘

- 4002:雙4輸入反或閘

- 4078:單8輸入反或閘

- TTL

- 7402:四2輸入反或閘

- 7427:三3輸入反或閘

- 7425:雙4輸入反或閘(有閘門,已不再使用)

- 74260:雙5輸入反或閘

- 744078:單8輸入反或閘

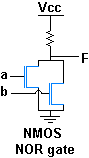

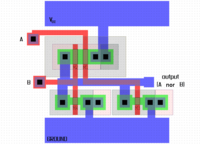

實現[編輯]

|

|

上圖展示了使用NMOS線路的2輸入反或閘的構造。如果輸入都是高電平,對應的NMOS就會接通,輸出會被拉到低電平;反之輸出會通過上拉電阻被拉到高電平。下圖展示了使用CMOS技術的2輸入反或閘。輸出端的二極體和電阻用來保護CMOS元件,以防其受到靜電放電(ESD)的損害,從而在電路的邏輯功能中發揮不了作用。

備選方案[編輯]

如果沒有專門的反或閘,可以用反及閘實現反或閘,方法是將兩個輸入接在一起的反及閘作為另外一個反及閘的兩個輸入,然後在後者的輸出接一個輸入接在一起的反及閘,即可實現反或閘。任何邏輯閘都可以用反及閘的組合或反或閘的組合實現。

反或邏輯[編輯]

反及閘實現的反或閘邏輯函數如下:

反或閘具有函數完備性,和反及閘一樣可以僅用其實現其他所有的邏輯功能。

| NOT(非) | |||

| AND(與) | |||

| NAND(與非) | |||

| OR(或) | |||

| NOR(或非) | |||

| XOR(互斥或) | |||

| XNOR(同或) | |||

| 蘊涵 | |||

| 等價 | |||

| 重言式 | |||

| 矛盾式 |

參見[編輯]

| |||||||||||||||||

| |||||||||||||||||||||||||||||

![{\displaystyle x{\overline {\lor }}y=\left[\left(x{\overline {\land }}x\right){\overline {\land }}\left(y{\overline {\land }}y\right)\right]{\overline {\land }}\left[\left(x{\overline {\land }}x\right){\overline {\land }}\left(y{\overline {\land }}y\right)\right]}](https://wikimedia.org/api/rest_v1/media/math/render/svg/38fd5c77550c8a7d8c14d77bc5d4f8217dd70e64)

![{\displaystyle \left[\left(x{\overline {\lor }}x\right){\overline {\lor }}\left(y{\overline {\lor }}y\right)\right]{\overline {\lor }}\left[\left(x{\overline {\lor }}x\right){\overline {\lor }}\left(y{\overline {\lor }}y\right)\right]}](https://wikimedia.org/api/rest_v1/media/math/render/svg/dba7191b0cae3237e54871465a794c731d51ae2a)

![{\displaystyle \left(x{\overline {\lor }}y\right){\overline {\lor }}\left[\left(x{\overline {\lor }}x\right){\overline {\lor }}\left(y{\overline {\lor }}y\right)\right]}](https://wikimedia.org/api/rest_v1/media/math/render/svg/0f22f755c9703bfca74d5fff0656b1879fc8189a)

![{\displaystyle \left[\left(x{\overline {\lor }}y\right){\overline {\lor }}x\right]{\overline {\lor }}\left[\left(x{\overline {\lor }}y\right){\overline {\lor }}y\right]}](https://wikimedia.org/api/rest_v1/media/math/render/svg/b18aa26772bf982a90a7400a077c7f8482e15eee)

![{\displaystyle \left[\left(x{\overline {\lor }}x\right){\overline {\lor }}y\right]{\overline {\lor }}\left[\left(x{\overline {\lor }}x\right){\overline {\lor }}y\right]}](https://wikimedia.org/api/rest_v1/media/math/render/svg/a106b94d42c28f1fa6c0563b3368990dbd50328b)

![{\displaystyle \left[x{\overline {\lor }}\left(y{\overline {\lor }}y\right)\right]{\overline {\lor }}\left[x{\overline {\lor }}\left(y{\overline {\lor }}y\right)\right]}](https://wikimedia.org/api/rest_v1/media/math/render/svg/60e3aada2cf1d960dcd7ae9e5b7b1d43566b61ad)

![{\displaystyle \left[\left(x{\overline {\lor }}x\right){\overline {\lor }}x\right]{\overline {\lor }}\left[\left(x{\overline {\lor }}x\right){\overline {\lor }}x\right]}](https://wikimedia.org/api/rest_v1/media/math/render/svg/8bc335e3197d5f3f0f9ecc80aa666768f9b0929d)